Arhitekture i organizacije računara Pregled

21. septembar 2005. god. Pismeni ispit iz Arhitekture i organizacije računara

3. zadatak

Dat je sledeći niz instrukcija u MIPS arhitekturi. Navesti zavisnosti po

podacima u datom nizu instrukcija i prikazati izvršenje ovog niza instrukcija na

petostepenom protočnom procesoru po taktnim ciklusima za sledeća dva slučaja: a)

bez premošćavanja, uz pretpostavku da se grananje nikada ne obavlja, i grananje u

četvrtoj instrukciji nije obavljeno, i b) sa premošćavanjem, uz pretpostavku da se

grananje nikada ne obavlja, i grananje u četvrtoj instrukciji je obavljeno.

Resenje:

Za protočni procesor sa razrešenjem ishoda grananja u ID stepenu. Bez premošćavanja sa izlaza EX/ME

protočnog registra na ulaz bloka Zero u ID stepenu.

Podsetimo se da se u MIPS arhitekturi pri pribavljanju svih instrukcija, pa i instrukcija uslovnog

grananja, PC inkrementira za dužinu instrukcije, odnosno 4 bajta. Ako je uslov grananja ispunjen,

ažuriranom sadržaju PC-a dodaje se četvorostruka vrednost pomaka. U instrukciji BEZ R5, 3, sa adresom

x+12, to vodi prelasku na instrukciju sa adresom x+12+4+3

4=x+28. Sadržaj registra R0 je fiksiran na nuli,

tako da instrukcija BEZ R0, 2 ustvari predstavlja instrukciju preskoka dve sledeće insrukcije:

x+24+4+2

4=x+36.

Hazardi tipa “čitanje nakon upisa” javljaju se između instrukcija (2,3), (3,4), (8,9) i (8,10).

a)

Izvršenje niza instrukcija bez premošćavanja, uz pretpostavku da se grananje ne obavlja, grananje

neobavljeno.

Ovde se javlja hazard tipa RAW između instrukcija ANDI i BEZ preko registra R5. Za kompletiranje

instrukcije grananja u ID fazi potreban je ceo taktni ciklus. Kako ANDI instrukcija u svojoj WB fazi upisuje

rezultat u prvoj polovini taktnog ciklusa, ostavljajući samo polovinu taktnog ciklusa za kompletiranje ID faze

instrukcije BEZ, što nije dovoljno, to se ID faza instrukcije BEZ nastavlja i u sledećem taktnom ciklusu.

b)

Izvršenje niza instrukcija sa premošćavanjem, uz pretpostavku da se grananje ne obavlja, grananje

obavljeno.

ADD R1,R2,R3

SUBU R2,R4,R3

ANDI R5,R2, #511

BEQ R5, 3

SW R2, 12(R7)

ADD R3,R6,R2

BEQ R0, 2

LW R4, 20(R7)

SUBU R8, R4 ,R10

ANDI R1, R4 , #16

Taktni ciklusi (TC)

Adresa

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16 17 18 19

x

ADD R1,R2,R3

F

D

E M W

x+4 SUBU

R2

,R4,R3

F

D

E M W

x+8 ANDI

R5

,

R2

, #511

F

D •D •D E M W

x+12 BEZ

R5

, 3

F •F •F D •D •D •D

x+16 SW R2, 12(R7)

F •F •F •F D

E M W

x+20 ADD R3,R6,R2

F

D

E M W

x+24 BEZ R0, 2

F

D

x+28 LW

R4

, 20(R7)

F

x+32 SUBU R8,

R4

,R10

x+36 ANDI R1,

R4

, #16

F

D

E M W

Oktobar 2005. god. Pismeni ispit iz Arhitekture i organizacije računara

.

3. zadatak

Dat je sledeći niz instrukcija u MIPS arhitekturi. Navesti zavisnosti po

podacima u datom nizu instrukcija i prikazati izvršenje ovog niza instrukcija na

petostepenom protočnom procesoru (sa razrešenjem ishoda grananja u ID stepenu) po

taktnim ciklusima za sledeća dva slučaja: a) bez premošćavanja, uz pretpostavku da se

grananje uvek obavlja, i grananje u četvrtoj instrukciji nije obavljeno, i b) sa

premošćavanjem, uz pretpostavku da se grananje uvek obavlja, i grananje u četvrtoj

instrukciji je obavljeno. Nema premošćavanja sa izlaza EX/ME protočnog registra na

ulaz bloka Zero u ID stepenu.

Maja 2006. god. Drugi kolokvijum iz Arhitekture i organizacije računara

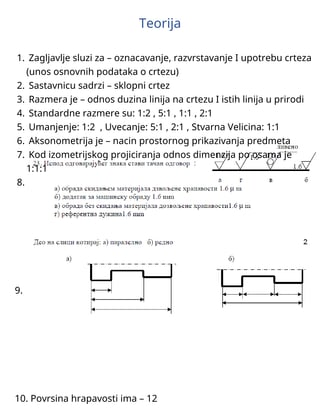

6. Dat je deo programa:

Pretpostaviti da je početni sadržaj R6 = R9+45. U ovom zadatku

koristiti protočni procesor sa hardverom za razrešenje ishoda grananja u

ID stepenu i pretpostaviti da obraćanja memoriji ne unose zastoje.

a.

Navesti zavisnosti po podacima prisutne u datom programu.

b.

Prikazati vremenski dijagram izvršenja ovog niza instrukcija pri

postojanju hardvera za premošćavanje. Za svako premošćavanje ukazati

na taktni ciklus u kome se ono vrši, kao i na protočni stepen iz koga se

podatak za premošćavanje uzima i protočni stepen kome se podatak

dostavlja. Pretpostaviti da se grananjima rukuje predviđanjem da će biti

obavljena. Koliko taktnih ciklusa zahteva izvršenje petlje?

Taktni ciklusi (TC)

Adresa

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16 17 18

x

ADD R1,R2,R3

F

D

E M W

x+4 SUBU

R2

,R4,R3

F

D

E <M W

x+8 ANDI

R5

,

R2

, #511

F

D >E M W

x+12 BEZ

R5

, 3

F

D •D •D •D

x+16 SW R2, 12(R7)

F •F •F •F

x+20 ADD R3,R6,R2

x+24 BEZ R0, 2

x+28 LW

R4

, 20(R7)

F

D

E M <W

x+32 SUBU R8,

R4

,R10

F

D •D >E M W

x+36 ANDI R1,

R4

, #16

F •F D

E M W

ADD R1,R2,R3

SUBU R2,R4,R3

ANDI R5,R2, #511

BEQ R5, 3

SW R2, 12(R7)

ADD R3,R6,R2

BEQ R0, 2

LW R4, 20(R7)

SUBU R8, R4 ,R10

ANDI R1, R4 , #16

loop:

(1) LW R1, 16 (R3)

(2) ADD R2, R1, R7

(3) SUB R4, R2, R8

(4) LW R4, 24 (R2)

(5) ADD R7, R5, R4

(6) SUBI R6, R6, #5

(7) SUB R5, R6, R9

(8) BNZ R5, loop

(9) SLL R10, R9, 4

Želiš da pročitaš svih 9 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.