VHDL sinteza Pregled

VHDL RTL синтеза

Увод

• Постоји неколико алата за синтезу које

праве различити произвођачи.

• Они се разликују у скуповима команди и

начину на који задајемо ограничења у

синтези.

• Већина прихвата једино дизајн описан на

нивоу трансфера међу регистрима (RTL) и

генерише кола састављена од логичких

гејтова и флип-флопова.

• Ове разлике су мотивисале састављање

IEEE стандарда 1076.6, Стандард за VHDL

Register Transfer Level синтезу.

Типови података

• Стандардом су дозвољени само следећи типови:

– Типови набрајања, укључујући предефинисане типове

boolean, bit и character.

– Целобројни типови, укључујући предефинисане типове

integer, natural i positive.

– Једнодимензионални низови скалара и предефинисаних

типовова bit_vector и string

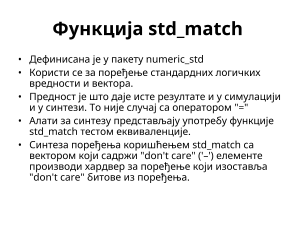

– std_ulogic, std_ulogic_vector, std_logic и std_logic_vector,

дефинисани у пакету std_logic_1164

– unsigned и signed, дефинисани у пакету numeric_bit

– unsigned и signed, дефинисани у пакету numeric_std

Имплементација

скаларних типова

• Предефинисани типови boolean и bit,

као и стандардни логички типови

std_logic и std_ulogic имплементирају

се у хардверу као појединачни

битови.

Имплементација

скаларних типова

•

Целобројни типови се имплементирају као

вектор битова.

•

Ако тип обухвата негативне вредности,

користи се означено кодирање у

комплементу двојке:

type

sample

is range

–64

to

63

;

—7-битно кодирање у комплементу двојке

subtype

table_index

is

natural

range

0

to

1023

;

— 10-битно неозначено

кодирање

•

Алати који се придржавају стандарда треба

да подржавају целе бројеве у опсегу –2

31

до

+2

31

– 1

Želiš da pročitaš svih 44 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.