ARM7 procesor Pregled

SEMINARSKI RAD

ARM7 procesor

Namenski mikroprocesorski sistemi

Profesor:

Student:

2

Sadržaj

Uvod – 3

Arhitektura ARM procesora – 4

Razvojni alati ARM – a -5

Organizacija i implementacija ARM – a – 6

ARM jezgra procesora – 8

Hardver i softver – 10

Zaključak – 15

Literatura - 16

4

Arhitektura ARM procesora

U vreme kada se pojavio ARM čip, jedino raspoložive RISC arhitekture su bile

RISC I razvijen na Berkeley-u i MIPS na Stanfordu.

ARM arhitektura je prihvatila brojne osobine RISC I dizajna, ali je brojne odbacila.

One koje su se i dalje koristile su bile:

· Napuni - smesti arhitektura (load-store)

· 32-bitni fiksni format instrukcija

· Troadresni format instrukcija

Osobine koje je ARM odbacio, a bile su korišćene na RISC I arhitekturi su:

-

Rad sa registarskim prozorima

-

Odloženo grananje

-

Izvršenje svih instrukcija u jednom ciklusu.

Skup instrukcija jednog procesora definiše operacije koje programer koristi da promeni

stanje sistema. Stanje čine vrednosti podataka koji se čuvaju u vidljivim registrima

procesora i u sistemskoj memoriji. Svaka instrukcija izvršava definisanu transformaciju

procesora iz stanja koje je bilo pre instrukcije, u stanje po njenom okončanju. Promena

stanja se odnosi samo na programsko vidljive, a ne nevidljive registre.To znači da su

bitne samo vrednosti koje se čuvaju u vidljivim registrima.

5

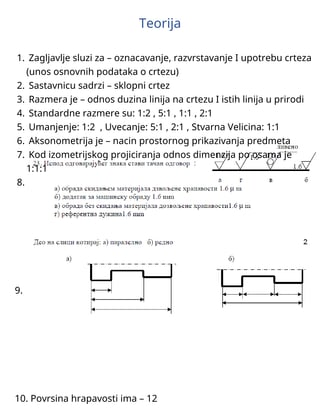

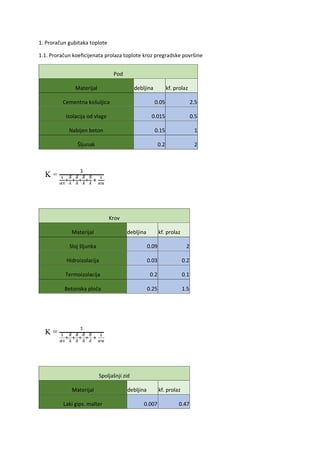

Programersko vidljivi registri ARM7 procesora

Statusni registar tekućeg programa (CPSR) se koristi za čuvanje statusnih markera. Ovi

markeri se postavljaju nakon izvršenja aritmetičko - logičkih operacija. Sadržaj ovih

bitova definiše režim rada procesora, način prihvatanja prekida i stanje nakon izvršenja

operacija. Registri R0 do R12 su registri opšte namene, R13 se koristi kao pokazivač

magacina, R14 kao registar za povezivanje potprograma, a R15 kao programski brojač.

ARM je arhitektura tipa Load - Store. To znači da sve aritmetičko - logičke instrukcije

manipulišu nad sadržajem registara, a jedine dve instrukcije pomoću kojih se vrši

obraćanje memoriji su operacije

Load i Store.

Pomoću

Load

se dobavlja podatak iz

memorije u registar, a pomoću

Store

sadržaj registra se smešta u memoriju.

Sve ARM instrukcije su 32-bitne. Najznačajnije osobine skupa instrukcija ARM

procesora su sledeće:

·

Učitaj - smesti arhitektura

·

3 - adresne instrukcije za obradu podataka

·

uslovno izvršenje svake od instrukcija.

·

uključenje vrlo jakih višestrukih učitaj - smesti instrukcija registara

·

mogućnost da se izvedu opšte operacije pomeranja kao i opšte aritmetičko

-logičke operacije u jednoj instrukciji, koja se izvršava u jednom taktnom ciklusu

·

proširenje na otvoreni skup instrukcija preko skupa instrukcija koprocesora, što

uključuje i dodavanje novih registara i tipova podataka programerskom modelu.

·

16-bitna predstava skupa instrukcija velike gustine u Thumb arhitekturi.

ARM upravlja U/I periferijama (disk kontrolerima, mrežnim interfejsima) kao memorijski

mapiranim uređajima sa podrškom za prekide. Unutrašnji registri u ovim uređajima se

javljaju kao lokacije koje se mogu adresirati unutar memorijske mape ARM-a. Registri

mogu biti čitani ili zapisivani pomoću istih učitaj – smesti instrukcija kao i bilo koja druga

memorijska lokacija.

Razvojni alati ARM – a

Razvoj softvera za ARM je podržan odgovarajućim izborom alata koje je razvila

kompanija ARM Limited, ali postoji i mnogo drugih dostupnih alata nezavisnih od ove

kompanije.

Pošto se ARM koristi kao

embedded

kontroler kod kojih ciljni hardver nije

projektovan da predstavlja podlogu za razvoj softvera, ovi alati su namenjeni za razvoj

drugih arhitektura kakve su platforme PC-a na kojima se izvršavaju Windows programi

ili radne stanice koje rade pod UNIX-om. C-ovi ili izvorni asemblerski fajlovi se

Želiš da pročitaš svih 16 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.