RS Flip-Flop Pregled

BOSNA I HERCEGOVINA

FEDERACIJA BOSNE I HERCEGOVINE

UNSKO – SANSKI KANTON

OPĆINA CAZIN

PRVA SREDNJA ŠKOLA

MATURSKI RAD

PREDMET: DIGITALNA ELEKTRONIKA

TEMA: RS FLIPFLOP

Učenik: Mentor:

Ljubijankić Tarik prof. Čajić Idriz

Cazin, maj 2018. godine

SADRŽAJ

2. FLIPFLOP

SR flip-flop ima dva ulaza S i R po kojima je i dobio ime. Ulaz S se naziva setujući ulaz

(eng.

set

- postaviti), dok je ulaz R resetujući ulaz (eng.

reset

- poništiti).

Postavljanjem ulaza S u logičko stanje 1, a ulaza R u logičko stanje 0 izlaz Q se postavlja u

stanje 1, a izlaz Q' u stanje 0. Ukoliko se na ulaz S dovede logička 0, a na ulaz R logička 1 na

izlazu Q se dobije logička 0, a na izlazu Q logička 1.

Ako se na ulaze S i R istovremeno dovede logička 0, na izlazu se ne dešava nikakva promena,

dok se istovremenim dovođenjem logičke 1 uzrokuje nepredviđeno stanje na izlazu, pa se ova

kombinacija naziva zabranjeno stanje.

Rad flipflopa kao memorijskog elementa može da bude prikazan funkcionalnom tabelom ili

pomoću odgovarajućih jednačina prekidačke algebre. Funkcionalna tabela treba da sadrži sve

moguće kombinacije nezavisno promjenjivih veličina i odgovarajuće izlazne funkcije.

Najčešći način zapisivanja rada flip-flopa je korišćenjem ovakvih tabela stanja:

kola)

Eksitaciona<br>tabela

S

R

Q

n+1

Q Q

n+1

S R

Komentar

0

0

zadržava

stanje

0

0

0 X

nema

promene

0

1

Q = 0

1

0

0 1

reset

1

0

Q = 1

0

1

1 0

set

1

1

nestabilna

kombinacij

a

1

1

X 0

nedozvoljen

o stanje

Napomena: Znak „X“ označava da je signal proizvoljan

za datu kombinaciju na ulazu.

2.1 Logika RS flipflopa

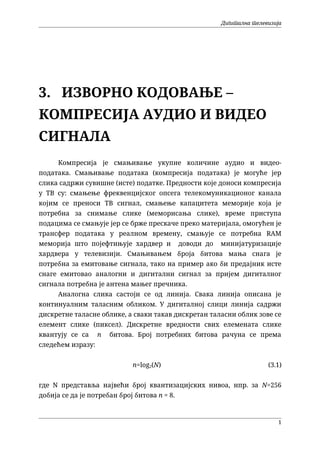

Simbol fliplopa koji je realizovan NILI kolima izgleda ovako:

Slika 2. Flipflop (NILI kola)

Jedan par ulaza NILI kola iskorišćen je za uspostavljanje pozitivne povratne sprege između

invertora, dok je drugi par rezervisan za ulazne priključke memorijskog elementa označene sa

R i S. Logička stanja kola koja se identifikuju prema nivou napona na izlazima Q i

Ǭ.

Uopšte je usvojeno da se se stanje flipflopa izražava logičkom vrijednošću napona na izlazu

Q. Kada tranzistor TR

2

vodi, izlaz Q je na niskom naponu, pa se tada kaže da je flipflop

resetovan. Da bi se ostvarilo takvo stanje kola, obavezno je da se na ulaz R dovede visoki

napon.

S druge strane, kada je tranzistor TR

2

zakočen, na izlazu Q je visoki napon, pa se tada kaže da

je flipflop setovan. Ovakvo stanje ostvaruje se dovođenjem visokog napona na ulaz S.

Očigledno je da izlaz Ǭ flipflopa ima komplementnu vrijednost izraza Q. Osim toga treba

napomenuti da je stanje flipflopa nedefinisano ako se istovremeno eksituju oba ulaza, tj. ako

se eksituju i R i S ulaz.

Iz navedenog se može zaključiti da ovo kolo može da bude samo ili setovano ili resetovano, te

se zbog toga za ovakav memorijski element i kaže da ima RS logiku.

Pošto se kod ovih flipflopova operiše sa logičkim vrijednostima izraza Q u dva vremenska

intervala koji slijeduju jedan iza drugog, mora se uvesti i dopunska oznaka koja pokazuje na

Želiš da pročitaš svih 20 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.