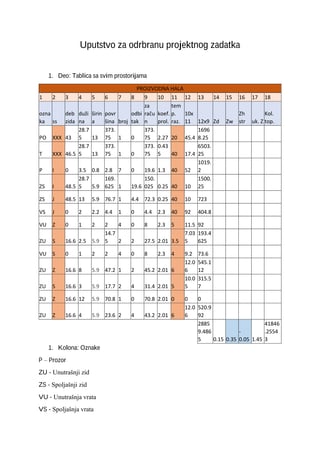

Standardni sekvencijalni moduli Pregled

1

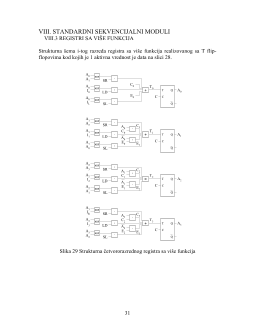

VIII. STANDARDNI SEKVENCIJALNI MODULI

VIII.1

REGISTRI

VIII.2

BROJA

Č

I

VIII.3 REGISTRI SA VIŠE FUNKCIJA

VIII.4

MEMORIJE

SA

RAVNOPRAVNIM PRISTUPOM

2

VIII. STANDARDNI SEKVENCIJALNI MODULI

VIII.1

REGISTRI

Registri su sekvencijalne mreže koje u digitalnim ra

č

unarima i drugim

digitalnim ure

đ

ajima služe za pam

ć

enje binarnih re

č

i.

Registar za pam

ć

enje binarne re

č

i dužine n bita može se posmatrati kao

sekvencijalna mreža sa n razreda. U registru postoji po jedan razred za svaki bit

binarne re

č

i, pa se registar može posmatrati kao n sekvencijalnih mreža.

Ako je oznaka registra A onda je najpogodnije i njegovo stanje ozna

č

iti sa

A

=

A

n-1

A

n-2

...A

0

gde su A

n-1

, A

n-2

, ..., A

0

razredi registra i koordinate vektora stanja.

Razmatraju se registri realizovani pomo

ć

u taktovanih flip-flopova.

Razmatraju se dve vrste registara i to:

registri

sa

paralelnim ulazima i izlazima i

registri sa serijskim ulazom i izlazom.

4

VIII. STANDARDNI SEKVENCIJALNI MODULI

VIII.1

REGISTRI

I

i

A

i

A

i

(t+1)

0 0

0

0 1

0

1 0

1

1 1

1

LD I

i

A

i

A

i

(t+1)

0 0 0

0

0 0 1

1

0 1 0

0

0 1 1

1

1 0 0

0

1 0 1

0

1 1 0

1

1 1 1

1

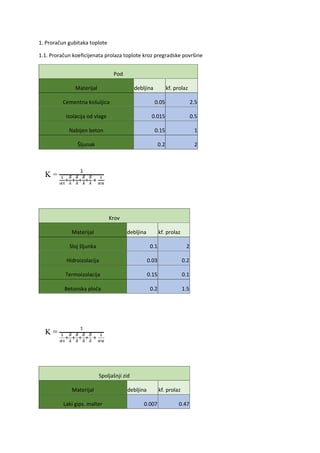

Slika 1 Tablica prelaza i-tog razreda

registra za slu

č

aja kada se upisom

upravlja pomo

ć

u signala takta

Slika 2 Tablica prelaza i-tog razreda

registra za slu

č

aja kada se upisom

upravlja nezavisno od signala takta

Na osnovu ovih tablica konstruiše se kombinacione tablice i odre

đ

uju funkcije

pobuda za razli

č

ite tipove flip-flopova.

Za D, T, RS i JK flip-flopove kod kojih je 1 aktivna vrednost ulaznih signala se

dobija:

1.

za

slu

č

aj kada se upisom upravlja pomo

ć

u signala takta

D

i

= I

i

T

i

= I

i

⊕

A

i

S

i

= I

i

, R

i

=

i

I

Ji = Ii, Ki =

i

I

2. za slu

č

aj kada se upisom upravlja nezavisno od signala takta

D

i

= LD I

i

+

LD

A

i

T

i

= LD (I

i

⊕

A

i

)

S

i

= LD I

i

, R

i

= LD

i

I

J

i

= LD I

i

, K

i

= LD

i

I

5

VIII. STANDARDNI SEKVENCIJALNI MODULI

VIII.1

REGISTRI

Realizacija i-tog razreda registra realizovanog koriš

ć

enjem D flip-flopa

1.

za

slu

č

aj kada se upisom upravlja pomo

ć

u signala takta data je na slici 3

2. za slu

č

aj kada se upisom upravlja nezavisno od signala takta data je na

slici4

A

i

D

Q

Q

D

C

D

i

.

LD

I

i

C

A

i

D

Q

Q

D

C

D

i

C

LD

.

I

i

.

+

Slika 3 Strukturna šema i-tog razreda

registra realizovanog koriš

ć

enjeg D

flip-flopa za slu

č

aj kada se upisom

upravlja pomo

ć

u signala takta

Slika 4 Strukturna šema i-tog razreda

registra realizovanog koriš

ć

enjeg D

flip-flopa za slu

č

aj kada se upisom

upravlja nezavisno od signala takta

7

VIII. STANDARDNI SEKVENCIJALNI MODULI

VIII.1

REGISTRI

Linije su A

n-1

, A

n-2

, ..., A

0

predstavljaju paralelne izlaze registra A.

Ako je potrebno,

č

itanjem se može upravljati pomo

ć

u upravlja

č

kog signala RD

(READ) kao što je prikazano na slici 6.

A

i

D

Q

Q

D

C

I

i

S

d

R

d

CL ST

D

i

.

LD

C

.

RD

Slika 6 Paralelno

č

itanje i-tog razreda registra A

Želiš da pročitaš svih 43 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.