Arhitektura mikrosistema Pregled

ARHITEKTURA MIKROSISTEMA

- materijal za pripremu ispita –

Pripremio: dr. Goran Lj.

Đ

or

đ

evi

ć

, predmetni nastavnik

2

4

2.3 VLSI tehnologije ....................................................................................................................................... 53

2.3.1 Tehnološko mapiranje za gejtovska polja.......................................................................................... 57

2.3.2 Tehnološko mapiranje za custom biblioteke...................................................................................... 63

2.4 Zaklju

č

ak ................................................................................................................................................... 66

3 Komponente digitalnih sistema ......................................................................................................................... 67

3.1 Kombinacione komponente....................................................................................................................... 67

3.1.1 Sabira

č

sa rednim prenosom .............................................................................................................. 67

3.1.2 Sabira

č

/oduzima

č

............................................................................................................................... 68

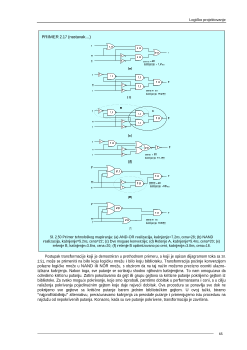

3.1.3 Logi

č

ka jedinica................................................................................................................................. 69

3.1.4 Aritmeti

č

ko-logi

č

ka jedinica ............................................................................................................. 70

3.1.5 Dekoderi...............................................................................................................................................73

3.1.5.1 Dekoderske mreže...................................................................................................................... 75

3.1.6 Mulitiplekseri..................................................................................................................................... 78

3.1.7 Magistrale .......................................................................................................................................... 80

3.1.8 Demultiplekser................................................................................................................................... 82

3.1.9 Koderi .................................................................................................................................................82

3.1.9.1 Binarni koderi ............................................................................................................................ 82

3.1.9.2 Prioritetni koderi ........................................................................................................................ 83

3.1.10 Komparatori magnitude ................................................................................................................... 86

3.1.10.1 Iterativne komparatorske mreže ............................................................................................... 88

3.1.10.2 Hijerarhijske komparatorske mreže ......................................................................................... 88

3.1.11 Kombinacioni pomera

č

i i rotatori.................................................................................................... 89

3.1.11.1 Barel pomera

č

.......................................................................................................................... 90

3.1.12 ROM memorije................................................................................................................................ 91

3.1.13 Programabilna logi

č

ka polja ............................................................................................................ 93

3.2 Sekvencijalne komponente ........................................................................................................................ 95

3.2.1 Le

č

kola i flip-flopovi ........................................................................................................................ 96

3.2.1.1 Le

č

kola...................................................................................................................................... 96

3.2.1.2 Flip-flopovi ................................................................................................................................ 98

3.2.2 Kona

č

ni automati............................................................................................................................. 104

3.2.3 Sinteza sekvencijalne logike ............................................................................................................ 105

3.2.3.1 Unos modela kona

č

nog automata ............................................................................................ 106

3.2.3.2 Minimizacija stanja .................................................................................................................. 107

3.2.3.3 Kodiranje stanja ....................................................................................................................... 109

3.2.3.4 Izbor memorijskih elemenata................................................................................................... 112

3.2.3.5 Optimizacija i tajming.............................................................................................................. 114

3.2.4 Memorijske komponente ................................................................................................................. 115

3.2.4.1 Registri ......................................................................................................................................115

3.2.4.2 Pomera

č

ki registri .................................................................................................................... 117

3.2.4.3 Broja

č

i...................................................................................................................................... 118

5

3.2.4.4 Registarski fajlovi .....................................................................................................................121

3.2.4.5 RAM memorija .........................................................................................................................123

3.2.4.6 Stek........... ................................................................................................................................127

3.2.4.7 FIFO..........................................................................................................................................131

3.2.5 Sekvencijalne staze podataka ...........................................................................................................134

3.2.6 Paralelne staze podataka ...................................................................................................................140

3.2.7 Projektovanje upravlja

č

ke jedinice...................................................................................................141

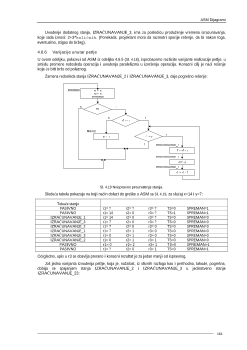

4 ASM Dijagrami................................................................................................................................................145

4.1 Stanja........................................................................................................................................................145

4.2 Komande ..................................................................................................................................................146

4.2.1 Postavljanje jednobitnih signala .......................................................................................................146

4.2.2 Postavljanje višebitnih signala..........................................................................................................146

4.2.3 Registarski prenos ............................................................................................................................147

4.3 Odluke........ ..............................................................................................................................................148

4.3.1 Relacije . ...........................................................................................................................................148

4.3.2 Eksterni statusi..................................................................................................................................149

4.4 Ulazi i izlazi ASM dijagrama ...................................................................................................................149

4.4.1 ASM ulazi.........................................................................................................................................150

4.4.1.1 Statusni ulazi.............................................................................................................................150

4.4.1.2 Ulazi podataka ..........................................................................................................................150

4.4.2 ASM Izlazi........................................................................................................................................151

4.4.2.1 Upravlja

č

ki izlazi......................................................................................................................151

4.4.2.2 Izlazi podataka ..........................................................................................................................151

4.5 Projektovanje ¨odozgo-naniže¨.................................................................................................................151

4.5.1 Opis ponašanja..................................................................................................................................152

4.5.2 Razrada........ .....................................................................................................................................152

4.5.3 Realizacija ........................................................................................................................................153

4.5.4 Automatsko projektovanje................................................................................................................153

4.6 Primer opisa ponašanja.............................................................................................................................153

4.6.1 Interfejs.............................................................................................................................................153

4.6.2 ASM sa ugra

đ

enim softverskim zavisnostima..................................................................................154

4.6.3 Eliminacija stanja TEST ...................................................................................................................157

4.6.4 Eliminacija stanja INIT ....................................................................................................................159

4.6.5 Pam

ć

enje koli

č

nika...........................................................................................................................159

4.6.6 Varijacije unutar petlje .....................................................................................................................161

4.6.7 Eliminacija stanja NULA3 ...............................................................................................................163

4.7 Primer razrade ..........................................................................................................................................165

4.7.1 Prvi primer........................................................................................................................................165

4.7.2 Drugi primer .....................................................................................................................................168

4.7.3 Tre

ć

i primer ......................................................................................................................................168

1

Principi digitalnog projektovanja

Napredak VLSI

1

tehnologije omogu

ć

io je proizvodnju mikro

č

ipova sa nekoliko miliona tranzistora. S obzirom

da je manuelno projektovanje u toj meri složenih integrisanih kola prakti

č

no nemogu

ć

e, napredak VLSI

tehnologije uslovio je tako

đ

e i pojavu industrije CAD

2

alata, koja se bavi razvojem softverskih sredstava i alata

za podršku projektovanju mikro

č

ipova. Kao rezultat toga, mnoge standardne tehnike digitalnog projektovanja

danas su ugra

đ

ene u CAD alate. Rastere

ć

en projektovanja na niskom nivou, projektant može slobodno da se

usredsredi na proces projektovanja u celini, po

č

ev od specifikacije zahteva do fabrikacije konkretnog proizvoda.

Me

đ

utim, sa tako širokim fokusom, savremeni projektanti su u poziciji da moraju vladati razli

č

itim tehnikama

kao što su tehnike za analizu i sprecifikaciju zahteva, modelovanje dizajna, softver-hardver kodizajn, sintezu,

verifikaciju, simulciju i testiranje mikro

č

ipova. U tom smislu, definicija pojma stru

č

njak za projektovanje

digitalnih kola i sistema je promenjena; to više nije ekspert za jednu konkretnu tehniku projektovanja, ve

ć

neko

ko poznaje principe projektovanja i koristi CAD alate u cilju istraživanja alternativnih rešenja i

implementacionih tehnika.

1.1 Reprezentacije

dizajna

Proces projektovanja svakog konkretnog proizvoda predstavlja složenu aktivnost u koju su, svako sa svojim

specifi

č

inim zadacima, uklju

č

eni razli

č

iti profili stru

č

njaka. Na primer, služba za marketing ispituje tržište i

postaljva zahteve koje novi proizvod treba da ispuni. Tehnolozi biraju implementacionu tehnologiju, sastavne

komponente i dobavlja

č

e tih komponenti. Grupa za podršku pribavlja ili razvija softverska sredstva koja

ć

e biti

koriš

ć

ena za projektovanje proizvoda i svakog njegovog dela. Projektanti preta

č

u polazne zahteve u proizvodnu

dokumentaciju. Test inženjeri osmišljavaju strategiju testiranja koja

ć

e omogu

ć

iti verifikaciju ispravnosti

projektovanog rešenja kao i ispravan rad gotovih proizvoda. Kona

č

no, inženjeri proizvodnje razvijaju plan

proizvodnje i prizvodnog procesa.

Svaka osoba uklju

č

ena u proces razvoja novog proizvoda, po

č

ev od definicije zahteva, preko projektovanja

do proizvodnje, na proizvod gleda iz svog, donekle razli

č

itog, ugla posmatranja i u svom radu koristi neke

specifi

č

ne informacije. Iz tog razloga, svaki proizvod, a time i svaki projekat, zahteva nekoliko razli

č

itih

reprezentacija ili pogleda, koji se razlikuju po tipu informacija koje sadrže i na koje se stavlja naglasak. Pored

toga, jedna ista reprezentnacija

č

esto zahteva razli

č

ite nivoe detaljnosti u razli

č

itim fazama projektnog ili

proizvodnog ciklusa. Tri tipa reprezentacija koje su naj

č

eš

ć

e u upotrebi su: bihejvioralna, strukturna i fizi

č

ka

reprezentacija.

Bihejvioralna ili funkcionalna reprezentacija je ona koja na projekat gleda kao na crnu kutiju i fokusira

se na opis njegovog ponašanja u funkciji ulaza i proteklog vremena. Drugim re

č

ima, bihejvioralna

reprezentacija opisuje funkcionalnost, ali ne i realizaciju konkretnog dizajna. Ova reprezentacija definiše

odziv crne kutije na bilo koju kombinaciju vrednosti ulaznih promenljivih, ali pri tome ništa ne kazuje o

tome kao napraviti crnu kutiju koriš

ć

enjem raspoloživih komponenti.

Strukturna reprezentacija je ona koja definiše crnu kutiju kao skup komponenti i njihovih veza. Za

razliku od bihejvioralne reprezentacije, ovde se opisuje realizacija proizvoda, ali bez direktnog pozivanja na

njegovu funkcionalnost. Naravno, u nekim slu

č

ajevima, funkcionalnost se može odrediti na osnovu funkcije

sastavnih komponenti. Me

đ

utim, doku

č

iti funkciju nekog sistema na ovaj na

č

in je teško i podložno

greškama. Funkcionalnost komponente ne mora biti u potpunosti iskoriš

ć

ena ili može biti izmenjena nekim

specifi

č

nim kodiranjem njenih ulaza i izlaza. Tako

đ

e, u slu

č

ajevima kada je broj komponenti veliki,

prakti

č

no je nemogu

ć

e otkriti njihovu zajedni

č

ku funkcionalnost, naro

č

ito danas kad tehnologija

omogu

ć

ava proizvodnju mikro

č

ipova sa nekoliko desetina miliona tranzistora.

1

VLSI(Very Large Scale Integration) je pojam koji ukazuje na integrisana kola veoma visokog stepena integracije.

2

CAD(Computer Aided Design) – projektovanje uz pomo

ć

ra

č

unara

Želiš da pročitaš svih 225 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.