Arhitektura računara Pregled

Архитектура рачунара

Одговори на питања са К2

(2009. 2012.)

Линкови:

●

рокови:

http://rti.etf.bg.ac.rs/rti/ef2ar/rokovi/

●

http://rti.etf.bg.ac.rs/rti/ef2ar/literatura/magistrala.pdf

●

http://rti.etf.bg.ac.rs/rti/ef2ar/literatura/ulaz_izlaz.pdf

1. Магистрала питања и одговори:

1.

Фебруар 2012/K2 2011/Јун 2010

:

ЗАВРШЕНО

Посматра се систем који се састоји из процесора, контролера за директни приступ меморији (DMA) и меморије повезаних магистралом у коме процесор управља

коришћењем магистрале. Навести сигнале које DMA и процесор размењују у ситуацијама када DMA жели да користи магистралу. Нацртати и објаснити

временске облике сигнала које том приликом DMA и процесор размењују за три карактеристичне ситуације.

Решење:

Сигнали које процесор и контролер размењују су:

●

hreq

овај сигнал контролер шаље када захтева магистралу да би реализовао неки циклус на њој

●

hack

овај сигнал процесор шаље контролеру када му одобри захтев за коришћење магистрале

Постоје три карактеристична случаја:

1.ни уређај ни процесор не чекају (контролер захтева да добије право на коришћење магистрале, а она је

већ слободна)

2.уређај чека процесор (контролер захтева да добије право на коришћење магистрале, али је она заузета)

3.процесор чека уређај (процесор хоће да реализује циклус на магистрали, али њу већ користи уређај)

2.

Јун 2011/Јул 2011/Септембар 2011/Јануар 2011/К2 2010/Јануар 2010/Септембар 2010/Октобар 2010

:

ЗАВРШЕНО

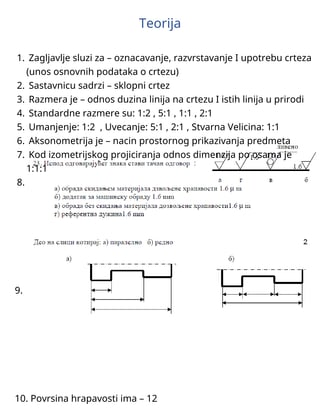

Нацртати и објаснити шему дела модула који се користи у арбитрацији са праћењем. Шема треба да укључи делове који подржавају и паралелну и серијску

арбитрацију, синхронизацију на сигнал такта магистрале и сигнал заузећа магистрале.

Решење:

Шема модула који се користи у арбитрацији са праћењем:

На магистралу су у општем случају везани различити уређаји. Истовремено магистралу може да користи један и

само један уређај. Ко добија магистралу на коришћење одређује специјални уређајконтролер који се назива

арбитратор. Арбитратор може да буде и процесор, па у том случају он одређује коме ће дати магистралу на

коришћење. На слици 8 је дат део модула који уређај користи да би послао захтев арбитратору и да би могао

да "обради одговор". Када је уређају потребна магистрала за реализацију неког циклуса, ово су кораци које

извршава:

● активном вредношћу сигнала

brqstart

уређај уписује у

BR

флипфлоп јединицу, па се на линији

BR

појављује јединица

● сигнал

BR

иде ка арбитратору и означава да је уређај затражио магистралу

● ако арбитратор одобри захтев уређају, преко линије

BG_IN

ће послати уређају јединицу, у супротном

шаље нулу

● сигнал

BG_OUT

се шаље наредном уређају у ланцу и активан је једино ако је добијена дозвола за

коришћење магистрале, али је претходни уређај у ланцу није захтевао (ако претходни уређај није

захтевао магистралу, #

BR

ће бити један, па се

BG_OUT

поставља исто на 1)

● затим, уређај који је добио магистралу на коришћење чека да се магистрала ослободи (можда још није

Želiš da pročitaš svih 9 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.