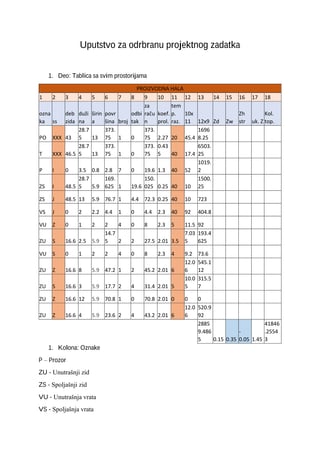

Magistrale Pregled

1

5. PRENOSNI PUTEVI IZME

Đ

U FUNKCIONALNIH JEDINICA

RA

Č

UNARSKOG SISTEMA

5.1. Osobine i klasifikacija ra

č

unarskih magistrala

Iz same definicije strukture ra

č

unarskog sistema i hijerarhijskih nivoa te strukture, uo

č

ava se

da je suštinsko pitanje redosled i na

č

in povezivanja pojedinih elementarnih komponenti. Ve

ć

na

nivou procesora, kao što je to opisano, formira se jedinstven prenosni put, interna magistrala,

radi izbegavanja velikog broja linija koje spajaju registre.

Na višem nivou strukture, potrebno je na efikasan na

č

in organizovati razmenu informacija

izme

đ

u pojedinih funkcionalnih jedinica ra

č

unarskog sistema. U tu svrhu, kao najefikasnije

rešenje, formira se jedinstven prenosni put, u obliku fizi

č

kog medijuma koji prenosi elektri

č

ne

signale – nosioce instrukcija i podataka. Ovaj skup zajedni

č

kih, deljenih sprežnih signala naziva

se

magistralom

ra

č

unarskog sistema. Da bi se naglasila njena suštinska razlika u odnosu na

internu magistralu, nekad se koristi i termin

spoljna magistrala

.

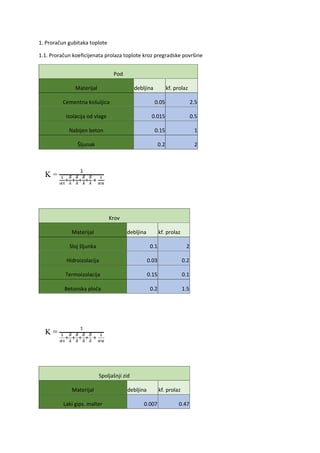

Slika 5.1 Magistralna organizacija ra

č

unarskog sistema

Magistrala me

đ

usobno povezuje centralni procesor, memoriju i periferijske U/I module, i

osnova je za izgradnju složenih ra

č

unarskih struktura.

O

č

igledna je pogodnost magistralne organizacije u pogledu cene i jednostavnosti relizacije,

kao i mogu

ć

nosti proširenja ra

č

unarskog sistema dodavanjem novih modula. Ukoliko je odre

đ

eni

tip magistrale standardizovan, to dodatno stvara mogu

ć

nost nesmetane upotrebe modula

razli

č

itih prizvo

đ

a

č

a.

Istovremeno, svaka magistrala unosi i odre

đ

ena ograni

č

enja u pogledu maksimalnih

performansi ra

č

unarskog sistema. To se odnosi pre svega na propusni opseg magistrale, koji

limitira maksimalnu brzinu komunikacije sa U/I periferijama. Istovremeno, elektri

č

ne osobine

magistrale definišu njenu najve

ć

u dužinu i broj modula koji se na nju mogu povezati.

Ure

đ

aji koji se povezuju preko magistrale, me

đ

usobno se vrlo razlikuju u pogledu kašnjenja

i brzine prenosa. Zato se uvode specijalizovane magistrale, pri

č

emu svaki tip magistrale mora

obezbediti mehanizme komunikacije koji

ć

e omogu

ć

iti adekvatno savladavanje ovih razlika.

Magistrale specijalizuju za specifi

č

nu namenu, ta

č

nije za odre

đ

en skup funkcionalnih

jedinica koje se na nju povezuju. Zato je uobi

č

ajeno razlikovanje

procesorske

,

sistemske

i

U/I

magistrale

, kod kojih, u iznetom redosledu, opada brzina prenosa i propusnost, a raste zna

č

aj

Sistemska magistrala

Procesor

Mrežni

adapter

Memorija

P

ro

ce

sor

sk

a m

a

g.

Video

kontroler

DVD

Disk

UI

m

a

g

is

tr

al

a

Serijski

adapter

Štampac

Spore UI

periferije

2

fleksibilnosti i proširivosti magistrale. Procesorska magistrala, nekad ozna

č

ena i kao lokalna,

mora biti najbrža, jer je posve

ć

ena komunikaciji procesora sa memorijom i grafi

č

kim video

kontrolerom. Sistemska magistrala povezuje procesor sa brzim periferijama, vitalnim za rad i

performanse ukupnog ra

č

unarskog sistema, naj

č

eš

ć

e sa spoljnim memorijama i brzim mrežnim

kontrolerima. Najsporija je U/I magistrala, namenjena sprezanju sa sporijim perifernim

jedinicama, raznovrsnim po tipu i funkciji.

U svetu postoji velik broj standarda za ra

č

unarske magistrale,

č

iji se izvori mogu svrstati u

tri grupe. U prvu grupu izvora spadaju tehni

č

ka rešenja odre

đ

enog proizvo

đ

a

č

a, koja se zbog

velike rasprostranjenosti i popularnosti usvajaju kao koriš

ć

en (

de facto

) standard. Najizrazitiji

primer ovakvog uvo

đ

enja standarda je svakako ISA magistrala IBM PC ra

č

unara, u svim svojim

varijantama (XT, AT). Drugi zna

č

ajan izvor standarda su tehni

č

ka rešenja pojedinih proizvo

đ

a

č

a

koja su prilago

đ

ena i od strane nacionalnih i me

đ

unarodnih organizacija za standarde predložena

kao zvani

č

an standard (npr. VME, Multibus II, itd.). Kona

č

no, tre

ć

i izvor standarda se javlja

kada grupe nezavisnih proizvo

đ

a

č

a opreme, motivisane posebnim interesima i nezavisno od

organizacija za standarde razvijaju i definišu standarde za svoje potrebe i stavljaju ih na

raspolaganje širem krugu korisnika (npr. PCI ili STD standard). Za proces standardizacije je

karakteristi

č

no da definisani standardi

č

esto nisu rezultat isklju

č

ivo radne snage tehni

č

kih

argumenata, nego su bitno uslovljeni i komercijalnim interesima velikih proizvo

đ

a

č

a, tehni

č

kim

zahtevima grupa i korisnika od posebnog interesa.

S obzirom da su magistrale namenjene funkciji prenosa informacija u okviru ra

č

unarskog

sistema, njihova osnovna obeležja su slede

ć

a:

•

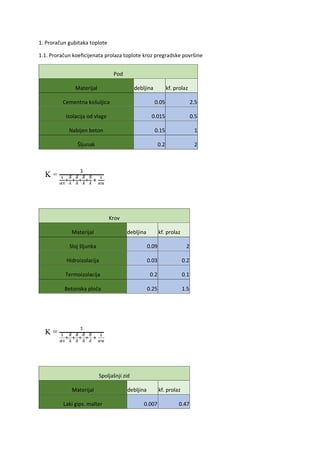

Širina magistrale

, iskazana u bitima, ukazuje na broj linija preko kojih se informacije

istovremeno prenose na magistrali. Širina adresne magistrale direktno odre

đ

uje

memorijski opseg koji je mogu

ć

e koristiti. Pri navo

đ

enju ovog parametra obi

č

no se misli

na širinu magistrale podataka, kao osnovnog za efikasnost konkretne magistrale.

•

Brzina magistrale

odre

đ

enja je u

č

estanoš

ć

u radnog takta, jer se obi

č

no u jednom taktu

preko jedne linije prenese jedan bit informacije. Ipak, postoje rešenja koja u istu svrhu

troše dva takta (ISA), ili naprotiv udvostru

č

avaju propusnost magistrale šalju

ć

i dva bita u

jednom taktu (AGP).

•

Propusnost magistrale

, ili njen prenosni opseg, odnosi se na opseg podataka koji se

teoretski može preneti preko magistrale u datom vremenu. Ovaj parametar se izvodi na

osnovu predhodno navedenih i daje zbirnu ocenu efikasnosti jedne magistrale.

Da bi se omogu

ć

io rast i nadgra

đ

ivanje sistema, i proizvo

đ

a

č

i i korisnici

č

esto pribegavaju

sprezanju magistrala niskog i visokog nivoa, tako da se podsistem konfigurisan oko magistrala

nižih nivoa tretira kao U/I jedinica sistema visokih performansi. Ovakav pristup ne samo da

omogu

ć

ava bezbolan prelaz na savršenije arhitekture uz o

č

uvanje najve

ć

eg dela po

č

etne

investicije, nego

č

esto predstavlja i preporu

č

ljivu strategiju razvoja novih sistema. U principu,

ova povezivanja realizuju se ili konvertorima brzina i protokola na magistrali, ili posredstvom

memorije sa dva pristupa.

5.2. Organizacija magistrale

Efikasno sprezanje centralnog procesora sa periferijama zahteva optimalno izvršenje U/I

aktivnosti, uz spre

č

avanje zagušenja na prenosnom putu. Šarolikost U/I ure

đ

aja u pogledu brzine

i režima prenosa podataka postavlja brojne probleme,

č

ije se rešenje naj

č

eš

ć

e traži u izdvajanju

pojedinih segmenata sprežne arhitekture i njihovoj specijalizaciji za deo zahtevanih funkcija. Ovi

segmenti predstavljaju autonomne celine, i kao takve se mogu izdvojeno i razmatrati.

4

transakcije, i signalima odziva prate

ć

e jedinice o uspešnosti prenosa. Skup pravila po kojima se

regulišu transakcije na magistrali, naziva se protokol magistrale.

Slika 5.3 Transakcija na magistrali

Pored pojedina

č

nog adresiranja, u sistemu izgra

đ

enom oko magistrale može biti podržano i

difuzno adresiranje, kojim se istovremeno adresira grupa modula. Pojedini sistemi omogu

ć

uju i

neke poboljšane tehnike adresiranja kao što su npr. poziciono (jednozna

č

no adresiranje

identi

č

nih modula koji se nalaze na razli

č

itim pozicijama u sistemu), odnosno logi

č

ko

(adresiranje globalnih memorijskih lokacija bez obzira na njihvou trenutnu fizi

č

ku poziciju u

sistemu).

Arbitriranjem se odre

đ

uje kojem modulu

ć

e se dodeliti magistrala u slu

č

aju da više modula istovremeno

ispostavi zahtev za dodelom magistrale. Arbitriranje može biti centralizovano ili decentralizovano. U

slu

č

aju centralizovanog, arbitriranje je povereno posebnoj komponenti koja prima i obra

đ

uje sve zahteve,

i vrši dodelu magistrale (

Slika 5.4). Rešenja koja se pri tome koriste, sli

č

na su onima razvijenim za potrebe sistema

prekida. Kod decentralizovanog arbitriranja, svi moduli lokalnim kolima prate zahteve svojih

konkurenata i preuzimaju kontrolu nad magistralom u slu

č

aju kada im je to dopušteno važe

ć

im

pravilima arbitriranja i dodeljenim prioritetom. Jedno od rešenja ove klase je i arbitracija sa

kolizijom, sli

č

no protokolu pristupa kod klasi

č

nog Ethernet-a.

Vode

ć

i

Prate

ć

i

Zahtev

Prenos podataka

Bus

Arbiter

M odul1

M odul

n

M odul2

Grant

Grant

Grant

Release

Request

Arbiter sa serijskom vezom m odula

Bus

Arbiter

M odul1

M odul n

M odul 2

G rant

Req

Arbiter sa paralelnom vezom modula

5

Slika 5.4 Centralizovano arbitriranje na magistrali

Prenos signala na magistralama može se odvijati asinhrono i sinhrono.

Asinhrone magistrale ne prenose takt i mogu prihvatiti ure

đ

aje najšireg opsega brzina

(naj

č

eš

ć

e klasi

č

ne periferijske U/I ure

đ

aje). Uspešan prenos podataka izme

đ

u asinhronih ure

đ

aja

(onih

č

iji taktovi nisu me

đ

usobno sinhronizovani), zahteva odgovaraju

ć

i fizi

č

ki protokol. Njegov

osnovni cilj je ozna

č

avanje trenutka pogodnog za transfer podataka, kao i perioda u kom je

generisana adresa ispravna (validna). Dve su osnovne tehnike za to: biranje (

strobing

) i

rukovanje (

hadshaking

).

Slika 5.5 Tehnika biranja (

strobing

)

Na prethodnoj slici je prikazana tehnika biranja, u varijantama kada prenos inicira odredišni

ili polazni ure

đ

aj. U prvom slu

č

aju, signal

strobe

prethodi slanju podataka od strane izvora. U

drugom slu

č

aju, izvor istim signalom ozna

č

ava validnost podataka na magistrali. Prednost ovog

metoda je jednostavnost, a osnovni nedostatak odsustvo odziva, odnosno bilo kakve indikacije o

uspehu prenosa. Dodatno, ukoliko je na magistralu vezano više ure

đ

aja, trajanje

strobe

-a mora

biti podešeno na nivo koji odgovara najsporijem ure

đ

aju.

Upravo je to razlog uvo

đ

enja tehnike rukovanja, koja koristi dva kontrolna signala:

ƒ

Zahtev

(

request

) kojim inicijator zahteva prenos podataka, i

ƒ

Odgovor

(

reply

) kojim prozvani ure

đ

aj ozna

č

ava svoju reakciju (vršenje transfera).

Zahvaljuju

ć

i ovim signalima, u toku transakcije se razlikuju

č

etiri stanja.

Slika 5.6 Redosled signala rukovanja pri prenosu koji inicira odredišni ure

đ

aj

Slika 5.6 prikazuje redosled akcija pri prenosu koji inicira odredišni ure

đ

aj:

1.

Odredište postavi

Zahtev

;

2.

Izvor pošalje podatke na magistralu;

3.

Posle kratkog

č

ekanja da se signali smire, izvor signalom

Odgovor

ozna

č

ava

prisustvo podataka;

Odrediste

Izvor

Strobe

DBUS

DBUS

Strobe

a) Prenos koji inicira odredisni uredjaj

Odrediste

Izvor

Strobe

DBUS

DBUS

Strobe

a) Prenos koji inicira izvor

Odrediste

Izvor

Zahtev

DBUS

DBUS

Zahtev

a) Prenos koji inicira odredisni uredjaj

Odgovor

Odgovor

7

Kod magistrala sa više potencijalnih vode

ć

ih modula, koristi se tehnika deljenja transakcije

(

split transactions

). Na taj na

č

in se izbegavaju

č

ekanja i maksimizira iskoriš

ć

enost propusnog

opsega magistrale. Osnovna ideja je u tome da se doga

đ

aji na magistrali podele na dva segmenta:

upit i odgovor. U vremenu izme

đ

u upita i odgovora, magistrala je raspoloživa za pokretanje nove

transakcije. Ovakvo rešenje se

č

esto naziva proto

č

nom magistralom, ili magistralom sa

distribucijom paketa.

Slika 5.9 Prenos podataka preko proto

č

ne magistrale

Pored pojedina

č

nog adresiranja, u sistemu izgra

đ

enom oko magistrale može biti podržano i

difuzno adresiranje (broadcast), kojim se istovremeno adresira grupa modula. Pojedini sistemi

omogu

ć

uju i neke poboljšane tehnike adresiranja kao što su npr. poziciono (jednozna

č

no

adresiranje identi

č

nih modula koji se nalaze na razli

č

itim pozicijama u sistemu), odnosno

logi

č

ko (adresiranje globalnih memorijskih lokacija bez obzira na njihvu trenutnu fizi

č

ku

poziciju u sistemu).

Od posebnog zna

č

aja za rad sistema je i mehanizam prekida kojim se podržava opsluživanje

vanrednih zahteva modula za koriš

ć

enjem magistrale. Za razli

č

ite realizacije magistrala, ovi

mehanizmi mogu biti veoma razli

č

iti po složenosti i performansi.

CLK

data

addr

wait

Active

w_l

Addr 1

RDATA1

WR DATA3

XXX

ADDR 2

RDATA2

ADDR 3

Želiš da pročitaš svih 36 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.