Simulacija projekta korišćenjem softvera MS Project 2003 Pregled

1

Uvod

VHDL (Very High Speed Integrated Circuits Hardware Description Language)

predstavlja programski jezik koji se koristi za opis hardvera. Koristi se za simulaciju i

za sintezu hardvera i to su dve oblasti primene VHDL-a kojima cemo se baviti u okviru

ovog dela kursa.

Osim VHDL-a, u upotrebi su i Verilog, AHDL, ABEL, Cupl i drugi programski jezici

u ovoj oblasti, ali se VHDL i Verilog najvise koriste.

VHDL pocinje da se razvija krajem 70-ih i pocetkom 80-ih. Danas, VHDL predstavlja

jezik pomocu kojeg se mogu opisati veoma slozeni procesi, hardverske arhitekture itd.

pa kao takav predstavlja industrijski standard u ovoj oblasti.

Razvoj VHDL-a kao standarda je poceo 1986. kada je predlozen prvi IEEE standard.

Posle nekoliko revizija, u decembru 1987. je usvojen IEEE 1076 standard. Ovaj

standard je 1993. imao reviziju, tako da je danas uglavnom u upotrebi IEEE 1076-1993

standard (krace VHDL93) iako je i posle toga nastavljan razvoj na ovom standardu

(poslednja revizija je bila 2002).

Iako VHDL predstavlja programski jezik i po elementima sintakse veoma podseca na

dobro poznate programske jezike (Pascal, C, C++ itd.), treba biti oprezan pri njegovom

razumevanju jer se on sustinski razlikuje. Osnovna razlika je u tome sto je VHDL u

sustini paralelan jezik, a ne samo strukturalan kao sto je recimo Pascal ili objektno

orijentisan kao sto je C++.

Pod pojmom paralelan se podrazumeva da se elementi VHDL programa u sustini

izvrsavaju paralelno (konkurentno, istovremeno) jer VHDL nastoji da opise fizicki

sistem, najcesce, neki digitalni sistem.

U strukturalnim programskim jezicima program se izvrsava po principu “naredba po

naredba” i na unapred predviden, sekvencijalan, nacin.

Digitalni sistemi gde recimo imamo vise ulaza u zavisnosti od kojih se menja izlaz,

nacin izvrsavanja VHDL programa koji opisuje takav sistem se znacajno razlikuje i ne

postoji pravilo po kojem se svaki program izvrsava, vec nacin izvrsavanja zavisi od

konkretnog programa. Kasniji primeri ce blize pojasniti nacin izvrsavanja VHDL

programa.

U realnim sistemima imamo odgovarajuca kasnjenja logickih kola i drugih elemenata

sistema, i njihovo modelovanje je omoguceno u VHDL-u.

Dakle, pomocu VHDL-a je moguce modelovanje veoma slozenih sistema i nivo dubine

opisa hardvera i abstrakcije zavisi iskljucivo od programera i njegove potrebe.

2

Nivoi modelovanja i apstrakcije

Kao sto je u uvodu receno, VHDL predstavlja univerzalan jezik za razlicite primene u

procesima opisa, modelovanja, simulacije i sinteze hardvera.

Nivoi modelovanja najcesce se dele u tri grupe:

Funkcionalni ili nivo ponasanja (behavior)

Strukturalni

Fizicki ili geometrijski

Ova podela nije striktna i razlikuje se u literaturi, ali sustina je slicna kod svih podela.

Nivoi modelovanja ujedno predstavljaju i nivoe abstrakcije. Pojam abstrakcije je

poznat i u strukturalnim programskim jezicima. Recimo, ako zelimo da uradimo

mnozenje dva broja to u C-u mozemo uraditi u jednom redu, iako se na konkretnom

hardveru - mikroprocesoru ta operacija izvrsava u vise perioda takta. Na taj nacin

programer ne mora detaljno da razmislja o konkretnom hardveru. Slicno, u VHDL-u

sto je neki nivo po svom opisu udaljeniji od konkretne hardverske implementacije to je

njegov nivo abstrakcije veci.

Prvi nivo opisuje ponasanje sistema i samim tim predstavlja najvisi nivo abstrakcije.

Drugi nivo modeluje strukturu sistema u smislu povezivanja pojedinih celina. Najnizi

nivo abstrakcije i najkonkretniji je fizicki nivo gde se programer moze spustiti do

fizickog nivoa - tranzistora, otpornika itd.

U okviru ovog kursa ce biti razmatrana samo prva dva nivoa, a konkretan nacin

implementacije hardvera ce biti prepusten softverskim alatima koji ce se koristiti.

Sledeci primer opisuje razlicite nivoe modelovanja i abstrakcije. Pretpostavimo da

treba da realizujemo mali elektronski digitalni sklop cija je funkcija da upozori vozaca

u automobilu da nije vezao pojas ili da su vrata otvorena. Ulazi u ovaj digitalni sistem

su: stanje motora (startovan ili ne), stanje vrata (otvorena ili ne) i stanje pojasa (vezan

ili ne).

Dakle upozorenje (izlaz naseg sklopa) se aktivira samo ako je motor startovan i pri

tome vozac ili nije vezao pojas ili nije vrata nisu zatvorena (ovo je vec opis ponasanja,

a koliko smo daleko od konkretne implementacije!).

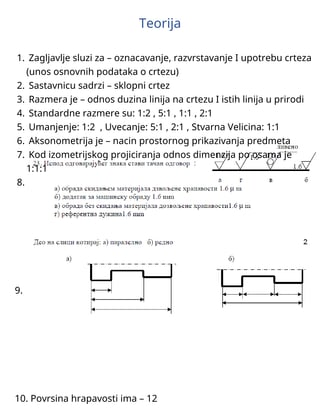

Ovaj tekstualni zapis se moze zapisati i algoritamski (slika 1), Bulovom algebrom

(slika 2), ili recimo tablicno (tabela 1), sto sve predstavljaju podnivoe prvog nivoa -

nivoa ponasanja.

Ukoliko sistem prikazemo crtanjem konkretnih logickih blokova i njih povezemo u

cilju dobijanja zeljene funkcije onda smo to uradili na strukturalnom nivou (slika 3).

4

Slika 3: Strukturalni zapis

Struktura VHDL programa

VHDL programi se sastoje iz tri dela:

deo za ukljucivanje biblioteka i paketa

deo koji opisuje entitet (entity) i

arhitekturnog dela

Za sada cemo razmatrati samo drugi i treci deo.

Drugi deo programa opisuje interfejs modula koji VHDL program opisuje. Dakle

interfejs prema spolja.

Ako zamislimo da VHDL program opisuje ponasanje jedne crne kutije, onda deo koji

opisuje entitet u stvari opisuje spoljasnje tacke (portove) preko kojih crna kutija

komunicira sa spoljnim svetom. (slika 4)

Treci deo programa, arhitekturni deo, opisuje nacin funkcionisanja entiteta definisanog

u prvom delu.

Arhitekturnih delova moze biti vise. Za sada cemo podrazumevati da je samo jedan

arhitekturni deo.+

5

Slika 4: Blok sema VHDL programa

Deklaracija entiteta

Kako bi izgledala deklaracija entiteta za nas primer?

Na ovom primeru

se vide neke od

osobina VHDL-a.

Komentari se pisu tako sto se ispred komentara stave dve crtice (--). Ovo je, na zalost,

jedini nacin pisanja komentara u VHDL-u, i jedna od mana ovog jezika je sto ne

postoje blok komentari, kao na primer u programskom jeziku C.

VHDL ne razlikuje mala i velika slova. Pri dodeljivanju imena promenljivama,

signalima i drugim identifikatorima mogu se koristiti samo alfanumericki simboli i

— primer deklaracije eniteta

entity

ALARM

is

port

(VRATA :

in

std logic;

POJAS :

in

std logic;

MOTOR :

in

std logic;

UPOZORENJE :

out

std logic);

end entity

ALARM;

7

Definisanje arhitekture

Opis ponasanja

Kako izgleda deo programa koji opisuje nacin ponasanja kola opisan pomocu Bulove

algebre (nivo ponasanja)?

Ovaj deo programa pocinje rezervisanom reci architecture nakon koje sledi ime. U

nasem slucaju to je behavioral jer smo rekli da je ovo opis sa nivoa ponasanja.

Na kraju se arhitektura asocira sa odgovarajucim entitetom (u nasem slucaju rec je o

entitetu ALARM). Blok definicije arhitekture pocinje sa begin, a zavrsava sa end (i

imenom). Izmedu begin i end se nalazi sve ono sto opisuje nacin ponasanja digitalnog

kola.

Osnovno sto nas interesuje kod digitalnih kola je kako se menjaju izlazi u zavisnosti od

ulaza. Ovde imamo samo jedan izlaz (UPOZORENJE) i njemu je dodeljen Bulov izraz

koji definise ponasanje ovog signala. Operator dodele vrednosti signalu je <=. Ostali

operatori su navedeni u poglavlju Izrazi i operatori.

architecture behavioral of ALARM

is begin

UPOZORENJE <= (

not

VRATA

and

MOTOR)

or

(

not

POJAS

and

MOTOR);

end architecture behavioral;

Želiš da pročitaš svih 47 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.