Arhitektura racunara Pregled

JOVAN

Đ

OR

Đ

EVI

Ć

ARHITEKTURA

RA

Č

UNARA

EDUKACIONI RA

Č

UNARSKI SISTEM

ARHITEKTURA I ORGANIZACIJA

RA

Č

UNARSKOG SISTEMA

Beograd 2002.

ii

4

PROCESOR ................................................................................................................... 41

4.1

O

PERACIONA JEDINICA

.............................................................................................. 41

4.1.1

Blok registri ...................................................................................................... 42

4.1.2

Blok operacije .................................................................................................. 50

4.1.3

Blok interfejs .................................................................................................... 57

4.1.4

Blok prekidi...................................................................................................... 66

4.2

U

PRAVLJA

Č

KA JEDINICA

............................................................................................ 72

4.2.1

Dijagram toka operacija ................................................................................... 72

4.2.2

Algoritam generisanja upravlja

č

kih signala ..................................................... 74

4.2.3

Realizacija upravlja

č

ke jedinice ..................................................................... 100

4.2.3.1

Oži

č

ena realizacija ..................................................................................... 100

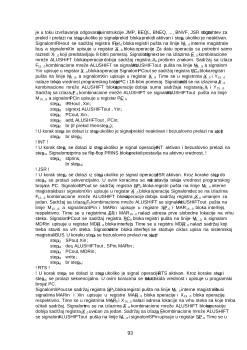

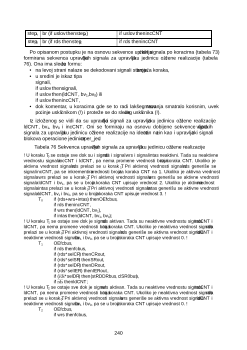

4.2.3.1.1 Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene

realizacije ............................................................................................. 100

4.2.3.1.2 Struktura upravlja

č

ke jedinice .............................................................. 116

4.2.3.2

Mikroprogramska realizacija ..................................................................... 123

4.2.3.2.1 Mikroprogramska realizacija sa mešovitim formatom mikroinstrukcije ...

............................................................................................................. 123

4.2.3.2.1.1 Format mikroinstrukcije ............................................................... 123

4.2.3.2.1.1.1 Operacioni deo mikroinstrukcije ........................................... 124

4.2.3.2.1.1.2 Upravlja

č

ki deo mikroinstrukcije .......................................... 131

4.2.3.2.1.2 Mikroprogram ............................................................................... 132

4.2.3.2.1.3 Struktura upravlja

č

ke jedinice ...................................................... 144

4.2.3.2.2 Mikroprogramska realizacija sa vertikalnim formatom mikroinstrukcija .

............................................................................................................. 150

4.2.3.2.2.1 Formati mikroinstrukcija .............................................................. 150

4.2.3.2.2.1.1 Operacione mikroinstrukcije .................................................. 151

4.2.3.2.2.1.2 Upravlja

č

ke mikroinstrukcije ................................................ 153

4.2.3.2.2.2 Sekvenca upravlja

č

kih signala po koracima za upravlja

č

ku jedinicu

sa vertikalnim formatom mikroinstrukcija ................................... 155

4.2.3.2.2.3 Mikroprogram ............................................................................... 164

4.2.3.2.2.4 Struktura upravlja

č

ke jedinice ...................................................... 175

4.2.3.2.3 Mikroprogramska realizacija sa nanoprogramiranjem ........................ 182

5

MEMORIJA ................................................................................................................. 195

5.1

OPERACIONA JEDINICA

............................................................................................. 195

5.2

UPRAVLJA

Č

KA JEDINICA

.......................................................................................... 198

5.2.1

Dijagram toka operacija ................................................................................. 198

5.2.2

Algoritam generisanja upravlja

č

kih signala ................................................... 199

5.2.3

Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene realizacije .. 202

5.2.4

Struktura upravlja

č

ke jedinice ........................................................................ 204

6

ULAZNO/IZLAZNI URE

Đ

AJI .................................................................................. 207

6.1

PERIFERIJA

............................................................................................................... 207

6.1.1

Operaciona jedinica ........................................................................................ 207

6.1.2

Upravlja

č

ka jedinica ...................................................................................... 209

6.1.2.1

Dijagram toka operacija ............................................................................. 210

6.1.2.2

Algoritam generisanja upravlja

č

kih signala ................................................ 211

iii

6.1.2.3

Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene realizacije .....

.................................................................................................................... 214

6.1.2.4

Struktura upravlja

č

ke jedinice .................................................................... 216

6.2

KONROLER PERIFERIJE BEZ DIREKTNOG PRISTUPA MEMORIJI

..................................... 218

6.2.1

Operaciona jedinica ........................................................................................ 218

6.2.1.1

Blok registri ................................................................................................ 219

6.2.1.2

Blok interfejs .............................................................................................. 224

6.2.2

Upravlja

č

ka jedinica ....................................................................................... 230

6.2.2.1

Upravlja

č

ka jedinica magistrale ................................................................. 231

6.2.2.1.1 Dijagram toka operacija ....................................................................... 231

6.2.2.1.2 Algoritam generisanja upravlja

č

kih signala ......................................... 232

6.2.2.1.3 Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene

realizacije .............................................................................................. 238

6.2.2.1.4 Struktura upravlja

č

ke jedinice .............................................................. 241

6.2.2.2

Upravlja

č

ka jedinica periferije ................................................................... 244

6.2.2.2.1 Dijagram toka operacija ....................................................................... 244

6.2.2.2.2 Algoritam generisanja upravlja

č

kih signala ......................................... 246

6.2.2.2.3 Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene

realizacije .............................................................................................. 252

6.2.2.2.4 Struktura upravlja

č

ke jedinice .............................................................. 256

6.3

KONTROLER PERIFERIJE SA DIREKTNIM PRISTUPOM MEMORIJI

.................................. 258

6.3.1

Operaciona jedinica ........................................................................................ 259

6.3.1.1

Blok registri ................................................................................................ 260

6.3.1.2

Blok interfejs .............................................................................................. 266

6.3.2

Upravlja

č

ka jedinica ....................................................................................... 277

6.3.2.1

Upravlja

č

ka jedinica magistrale ................................................................. 279

6.3.2.1.1 Dijagram toka operacija ....................................................................... 279

6.3.2.1.2 Algoritam generisanja upravlja

č

kih signala ......................................... 279

6.3.2.1.3 Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene

realizacije .............................................................................................. 285

6.3.2.1.4 Struktura upravlja

č

ke jedinice .............................................................. 288

6.3.2.2

Upravlja

č

ka jedinica periferije ................................................................... 290

6.3.2.2.1 Dijagram toka operacija ....................................................................... 290

6.3.2.2.2 Algoritam generisanja upravlja

č

kih signala ......................................... 292

6.3.2.2.3 Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene

realizacije .............................................................................................. 297

6.3.2.2.4 Struktura upravlja

č

ke jedinice .............................................................. 301

6.3.2.3

Upravlja

č

ka jedinica memorije ................................................................... 303

6.3.2.3.1 Dijagram toka operacija ....................................................................... 303

6.3.2.3.2 Algoritam generisanja upravlja

č

kih signala ......................................... 310

6.3.2.3.3 Sekvenca upravlja

č

kih signala za upravlja

č

ku jedinicu oži

č

ene

realizacije .............................................................................................. 331

6.3.2.3.4 Struktura upravlja

č

ke jedinice .............................................................. 338

7

LITERATURA .............................................................................................................. 341

1

1

KONFIGURACIJA SISTEMA

Ra

č

unarski sistem sadrži procesor CPU, memoriju MEM, ulazno/izlazne ure

đ

aje U/I,

ure

đ

aj za kontrolu ispravnosti rada sistema FAULT i sistemsku magistralu BUS (slika 1).

Arhitektura procesora od programski dostupnih registara ima registre opšte namene. Tipovi

podataka sa kojima se radi su celobrojne 16-bitne veli

č

ine sa znakom i bez znaka. Format

instrukcija je promenljiv tako da se u zavisnosti od tipa operacije koriste troadresni,

dvoadresni, jednoadresni i bezadresni formati instrukcija. Na

č

ini adresiranja uklju

č

uju

registarsko indirektno, registarsko indirektno sa pomerajem, memorijsko direktno, neposredno

i registarsko direktno adresiranje, pri

č

emu se prva

č

etiri na

č

ina adresiranja specificiraju

eksplicitno odre

đ

enim poljima instrukcije, dok se registarsko direktno adresiranje implicitno

koristi u aritmeti

č

kim instrukcijama, logi

č

kim instrukcijama i instrukcijama pomeranja i

rotiranja. Skup instrukcija uklju

č

uje instrukcije prenosa, aritmeti

č

ke instrukcije, logi

č

ke

instrukcije, instrukcije pomeranja i rotiranja kao i instrukcije skoka. Prekidi uklju

č

uju

unutrašnje i spoljašnje prekide sa maskiranjem i prioritiranjem prekida, kontekst procesora se

č

uva na steku, a adresa prekidne rutine utvr

đ

uje tehnikom vektorisanog mehanizma prekida.

Organizacija procesora je tako odabrana da je

č

ine dve odvojene jedinice i to operaciona

jedinica i upravlja

č

ka jedinica. Operaciona jedinica se sastoji od blokova registri, izvršavanje

operacija, povezivanje magistrale i opsluživanje prekida, me

đ

usobno povezanih internom

magistralom. Za prikazanu operacionu jedinicu procesora date su

č

etiri mogu

ć

e realizacije

upravlja

č

ke jedinice i to: oži

č

ena realizacija, mikroprogramska realizacija sa mešovitim

formatom mikroinstrukcija, mikroprogramska realizacija sa vertikalnim formatom

mikroinstrukcija i mikroprogramska realizacija sa vertikalnim formatom mikroinstrukcija i

nanoprogramiranjem.

Procesor po liniji inm dobija signal nemaskiraju

ć

eg zahteva za prekid od ure

đ

aja za

kontrolu ispravnosti rada sistema FAULT. Procesor po linijama

intr

1

,

intr

2

i

intr

3

dobija

signale maskiraju

ć

ih zahteva za prekid od ulazno/izlaznih ure

đ

aja U/I, a po linijama inta

1

,

inta

2

i inta

3

šalje signale dozvole prekida ulazno/izlaznim ure

đ

ajima U/I. Procesor po liniji

hldr

dobija signal zahteva koriš

ć

enja magistrale od ulazno/izlaznih ure

đ

aja U/I, a po liniji

hlda šalje signal dozvole koriš

ć

enja magistrale ulazno/izlaznim ure

đ

ajima U/I.

Memorija je kapaciteta 60K 16

−

bitnih re

č

i.

Ulazno/izlaznih ure

đ

aja ima 12 i to 8 sa kontrolerima bez direktnog pristupa memoriji i 4

sa kontrolerima za direktan pristup memoriji. Pošto procesor ima samo tri para linija

intr

1

i

inta

1

,

intr

2

i inta

2

i

intr

3

i inta

3

po kojima se izme

đ

u procesora i ure

đ

aja razmenjuju signali

zahteva za prekid i signale dozvole prekida, 12 ure

đ

aja je vezano u tri lanca sa po

č

etiri

ure

đ

aja u lancu.

Želiš da pročitaš svih 349 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.