Osnovni memorijski kola Pregled

УНИВЕРЗИТЕТ „ГОЦЕ ДЕЛЧЕВ“ ШТИП

В О Е Н А А К А Д Е М И Ј А

„Генерал Михаило Апостолски “- Скопје

-придружна членка-

(Катедра за Воени науки и воени вештини)

ИНДИВИДУАЛНИ РАД

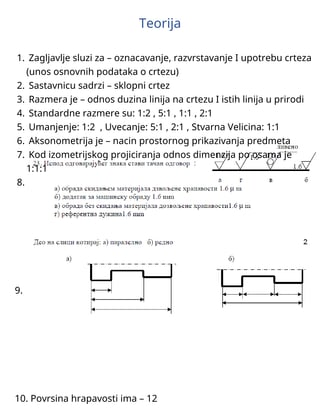

Предмет: Основе електронике

Тема: Основни меморијски кола

Предметен наставник:

Направио:

Д-р. Невен Трајчевски мај. доц.

питомец Душан Ќеќез

индекс бр. 1227

Скопје, април, 2016 година

2

:

Садржај

4

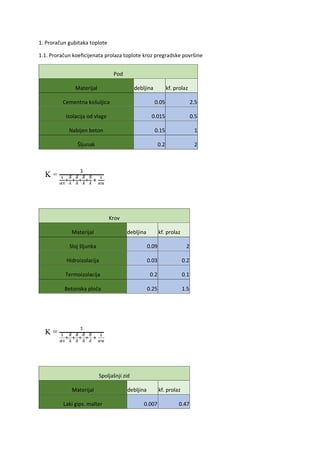

Постоје разне врсте и подјеле полупроводничких меморија.По једној од подјела

оне се дијеле на меморије код којих су процеси уписа и читања информација

равноправни ( red/write memory ) и меморије код којих је читање информација брзо а,

упис једнократан или дуготрајан ( read only memory –ROM ).Прва врста подјеле се

традиционално назива RAM ( random access memory- меморија са случајним

приступом ).Сами назив потиче од времена када се развијала рачунарска техника и

када се меморија са случајним приступом користила за меморија са магнетним

језгрима и полупроводничке меморије, које су омугућавале приступ до било које ћелије

у исто вријеме, за разлику од секвенцијалних меморија (CD,DVD,traka), код којих је

приступ информацијама најбржи када се оне читају редослиједом како су уписане.

По другој подјели,меморији се дијеле по способности чувања информација на статичке

меморије ( SRAM ) и динамичке меморије.

Статичке меморије задржавају уписане информације све док имају напајање или док

се не изврши поновни упис.

Динамичке меморије задржавају уписане информације веома кратко вријеме, реда

десетак ms, па се њихов садржај мора периодично обнављати.

Унутрашња структура меморијских кола

Памћење велике количине података захтјева одрећену организацију унутар

меморије. Структура ових меморија које раде на принципу адресирања је приказана на

слици:

Централни дио меморије је поље меморијских ћелија, које се састоји од потребног

броја елементарних меморија. Адерса ћелије којој се жели приступити улази у адресни

декодер преко адресног кола за спрегу ( bafer ). Улога декодера је селекотовање са

којом се жели остварити комуникација. Сложеност декодера расте са повећањем

бороја меморијских ћелија. Зато се елементарне меморије у матрични облик умјесто

линеарног распореда. У том случају адресирање се врши помоћу мања два декодера .

Укупан коришћени број логичких кола за реализацију та два декодера је мањи него у

случају једног декодера.

Унос података односно њихово ишчитавање се врши преко кола за спрегу за податке.

Обично се користе исте линије података за комуникацију у оба смјера. Прлииком уписа

подаци морају бири спремни неко вријеме, неспосредно прије уписа

Улога управљачке јединице је генерисање одређених одговарајућих управљачких

сигнала приликом уписа, читања или брисања за селектовану меморијску ћелију.

Иницијализација уписа се врши помоћу WE (engl.: write enable) сигнала који се шаље

управљачкој јединици меморије. За читање је потребно активирати сигнал OE (engl.:

output enable). Управљачка јединица посједује још један улаз са називом CS (engl.:

chip select) помоћу које је могуће покренути или зауставити рад читавог кола. Улога

овог улаза јесте да омогући проширрење капацитета меморије.

Želiš da pročitaš svih 14 strana?

Prijavi se i preuzmi ceo dokument.

Slični dokumenti

Ovaj materijal je namenjen za učenje i pripremu, ne za predaju.